Noticias

DAC explora el papel de la inteligencia artificial y el lavado de dinero en los mercados

Moscone Center, San Francisco, será el anfitrión del DAC del 25 al 28 de junio

Soluciones OneSpin y Austemper Design Systems Ambos destacarán las herramientas para la verificación de seguridad funcional. Austemper se centrará en el desarrollo de sistemas de misión crítica, con el conjunto de herramientas KaleidoScope que admite el diseño analógico para la propagación concurrente de fallas de señales mixtas. El conjunto de herramientas automatizadas tiene capacidades de análisis, síntesis y verificación de seguridad para aplicaciones orientadas a la certificación. Se utiliza para diseños automotrices a gran escala en ADAS y conducción autónoma. La simulación simultánea de fallas incluye simulaciones recomendadas por ISO 26262 para cumplir con los requisitos de ASIL.

Recientemente, la compañía se asoció con OneSpin Solutions para adoptar una metodología respaldada por herramientas para aplicaciones de seguridad funcional, combinando un flujo de diseño y verificación, que se demostrará en el stand de OneSpin. Los mecanismos de seguridad del hardware se insertan en los diseños de los chips y las herramientas de OneSpin Solutions verifican formalmente la lógica de seguridad del hardware. La comprobación de equivalencia garantiza que la lógica de seguridad insertada no afecte a la funcionalidad habitual y el análisis de detección de fallas verifica que los mecanismos de seguridad funcionen correctamente en caso de errores aleatorios.

OneSpin también promociona su kit de calificación de herramientas, luego de la verificación por parte de TÜV SÜD de sus procesos de desarrollo de herramientas. El kit inicial está disponible para la herramienta 360 EC-FPGA EDA de la compañía, una verificación automática de equivalencia secuencial que evita que los flujos de diseño de FPGA introduzcan errores de implementación. El kit está certificado según ISO 26262, IEC 61508 y EN 50128.

Información sobre FPGA

Aún con diseño FPGA, Plunificar ha colaborado con Xilinx para ofrecer el paquete de diseño Vivado en la nube, a través de la plataforma Plunify Cloud. Los diseñadores pagan tan solo 50 centavos para compilar un proyecto de Vivado en la nube de Amazon Web Services (AWS), incluidas las licencias.

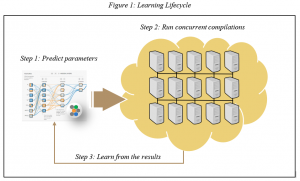

La compañía también demostrará mejoras en su software de sincronización de tiempo InTime para optimizar el tiempo FPGA en la nube (Figura 1). La Metodología de Optimización InTime puede mejorar la frecuencia del reloj en un 20 a 80% y cumplir los requisitos de tiempo en días, en lugar de semanas a través del aprendizaje automático. El software también acelera el cierre y la optimización del tiempo y se accede a través de la nube.

La compañía también demostrará mejoras en su software de sincronización de tiempo InTime para optimizar el tiempo FPGA en la nube (Figura 1). La Metodología de Optimización InTime puede mejorar la frecuencia del reloj en un 20 a 80% y cumplir los requisitos de tiempo en días, en lugar de semanas a través del aprendizaje automático. El software también acelera el cierre y la optimización del tiempo y se accede a través de la nube.

Promover la tecnología eFPGA, Achronix Semiconductor está colaborando con un especialista en IP EMITIR para aumentar el rendimiento y ahorrar en almacenamiento de memoria.

Los dos expositores explicarán cómo la IP de compresión sin pérdidas de CAST se ha trasladado a la cartera Achronix FPGA para su uso en aplicaciones de transferencia de datos de centros de datos y dispositivos móviles. La implementación de hardware del estándar de compresión sin pérdida para Deflate, GZIP y ZLIB es compatible con implementaciones de software usadas para compresión o descompresión para proporcionar un rendimiento de hasta 100 Gbit / s con baja compresión y baja latencia, junto con la tecnología Speedcore eFPGA para mover y almacenar grandes datos con un bajo consumo de energía.

CAST ha portado su IP a los FPGA de Achronix

Eficiencia energética

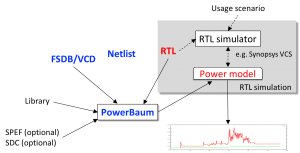

Hablando de administración de energía, otro expositor, Baum, identifica la eficiencia energética como el área menos desarrollada en el diseño de chips. Su herramienta de modelado y análisis de potencia automatizada está diseñada para proyectos de automoción, IoT, móviles, redes y servidores. PowerBaum 2.0 (Figura 3) admite alimentación dinámica y estática, teniendo en cuenta las descripciones RTL y de listas de conexiones, y agrega soporte para análisis de potencia con emulación de hardware. Esto, dice la compañía, permite a los ingenieros corregir errores de encendido en escenarios de software realistas. La herramienta también admite análisis con temperaturas arbitrarias que los diseñadores especifican para evaluar los efectos de la temperatura en el consumo de energía de un diseño.

En DAC, la compañía también presentará PowerWurzel, un motor de análisis de potencia de nivel de puerta para integrarse con PowerBaum para el modelado de energía.

Figura 3 Las herramientas de Baum analizan la eficiencia energética

Herramientas de verificación y diseño de SoC basadas en la nube para el diseño de IC de Métrica incluyen Cloud Simulator y Verification Manager, diseñados para administrar los requisitos y recursos de simulación, ajustándolos o disminuyéndolos cada minuto. La compañía afirma que Google Cloud permite una capacidad ilimitada de simulación SystemVerilog compatible con UVM y una gestión de verificación nativa basada en la web para tiempos de regresión más rápidos, reducción de errores de código troncal y cobertura de código predecible.

Además de los expositores, el evento organiza sesiones técnicas y un programa de conferencias magistrales sobre áreas temáticas. Este año, por ejemplo, Cadence albergará un tutorial sobre 'Seguridad y confiabilidad funcional para aplicaciones automotrices' y otro sobre aprendizaje automático ('Aprendizaje automático lleva el rendimiento del reconocimiento de voz al siguiente nivel'). Una conferencia de Anna-Katrina Shedletsky, Instrumental, el lunes 25 de junio, se centrará en "Automatización de la inteligencia: el aprendizaje automático y el futuro de la fabricación". El uso de ML y AI para la robótica socialmente asistida (SAR) es explorado en la conferencia magistral del jueves por Maja Matarić, Universidad del Sur de California, quien presentará 'Automatización vs Aumento: Robotocs Socialmente Asistencial y el Futuro del Trabajo'.

Otra nota clave aboga por RISC-V como un medio para liberar a los arquitectos de las arquitecturas de conjuntos de instrucciones patentadas (ISA). David A Patterson, Google y la Universidad de California, presentarán 'A New Golden Age for Computer Architecture: Aceleradores específicos de dominio y Open RISC-V'.

Una nueva área este año en DAC es el Design Infrastructure Alley. La iniciativa del Alianza ESD y Asociación para profesionales de informática de alto rendimiento es un área dedicada a la infraestructura de TI para el diseño de sistemas y componentes electrónicos. Además de los requisitos informáticos y de almacenamiento para el diseño y la gestión del uso de la nube, existe un pabellón dedicado al diseño en la nube que analiza la gestión de licencias, la computación grid y la seguridad de los datos.