# TwinDie<sup>TM</sup> RLDRAM 3

# MT44K64M18 – 2 Meg x 18 x 16 Banks x 2 Ranks MT44K32M36 – 2 Meg x 36 x 16 Banks

| Features                                                                                                                                              | Options • 168-ball FBGA package                                                                                                    | Marking    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|

| <ul><li> Uses 576Mb Micron RLDRAM 3 die</li><li> Organization</li></ul>                                                                               | <ul> <li>1.07ns and <sup>t</sup>RC (MIN) = 8ns<br/>(RL3-1866)</li> </ul>                                                           | -107E      |

| <ul> <li>32 Meg x 18 x 2 ranks</li> <li>32 Meg x 36 x 1 rank</li> <li>16 banks per die</li> </ul>                                                     | <ul> <li>1.07ns and <sup>t</sup>RC (MIN) = 10ns<br/>(RL3-1866)</li> </ul>                                                          | -107       |

| - Common I/O (CIO)                                                                                                                                    | <ul> <li>1.25ns and <sup>t</sup>RC (MIN) = 10ns<br/>(RL3-1600)</li> </ul>                                                          | -125E      |

| <ul> <li>1.2V center-terminated push/pull I/O</li> <li>2.5VV<sub>EXT</sub>, 1.35VV<sub>DD</sub>, 1.2VV<sub>DDQ</sub> I/O</li> </ul>                   | - 1.25ns and <sup>t</sup> RC (MIN) = 12ns<br>(RL3-1600)                                                                            | -125       |

| Description The 10h (This Distance Nigran's 570Mh                                                                                                     | <ul><li>Configuration</li><li>64 Meg x 18</li></ul>                                                                                | 64M18      |

| The 1Gb (TwinDie™) RLDRAM 3 uses Micron's 576Mb RLDRAM 3 die. Refer to Micron's 576Mb RLDRAM 3 data sheet for the specifications not included in this | <ul> <li>- 04 Meg x 16</li> <li>- 32 Meg x 36</li> <li>• Operating temperature</li> </ul>                                          | 32M36      |

| document. Specifications for base part number MT44K32M18 correlate to both TwinDie manufacturing part numbers MT44K64M18 and MT44K32M36.              | <ul> <li>Commercial (T<sub>C</sub> = 0° to +95°C)</li> <li>Industrial (T<sub>C</sub> = -40°C to +95°C)</li> <li>Package</li> </ul> | None<br>IT |

| nig pait numbers with the original and with the SZWISO.                                                                                               | <ul><li>168-ball FBGA (Pb-free)</li></ul>                                                                                          | RCT        |

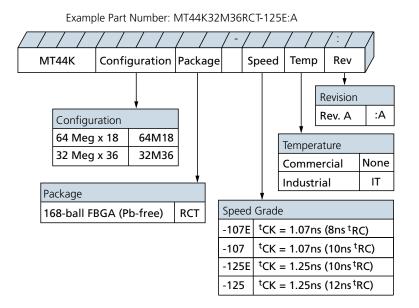

Figure 1: 1Gb RLDRAM 3 Part Numbers

### **BGA Part Marking Decoder**

Due to space limitations, BGA-packaged components have an abbreviated part marking that is different from the part number. Micron's BGA Part Marking Decoder is available on Micron's Web site at <a href="https://www.micron.com">www.micron.com</a>.

### 1.125Gb: x18, x36 TwinDie RLDRAM 3 Features

# **Contents**

| General Description                                              | 6  |

|------------------------------------------------------------------|----|

| Functional Block Diagrams                                        | 7  |

| Ball Assignments and Descriptions                                | 9  |

| Package Dimensions                                               |    |

| Electrical Characteristics - I <sub>DD</sub> Specifications      | 13 |

| Electrical Specifications – Absolute Ratings and I/O Capacitance | 15 |

| Absolute Maximum Ratings                                         | 15 |

| Input/Output Capacitance                                         | 15 |

| ODT Characteristics                                              | 16 |

| ODT Resistors                                                    | 16 |

| ODT Sensitivity                                                  | 18 |

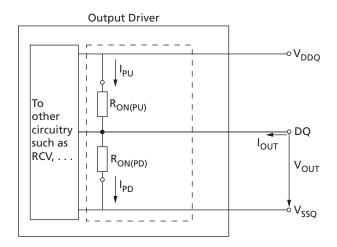

| Output Driver Impedance                                          | 18 |

| Output Driver Sensitivity                                        | 20 |

| Output Characteristics and Operating Conditions                  | 21 |

| Timing Adjustments                                               | 22 |

| Thermal Impedance Characteristics                                | 23 |

| Commands                                                         | 24 |

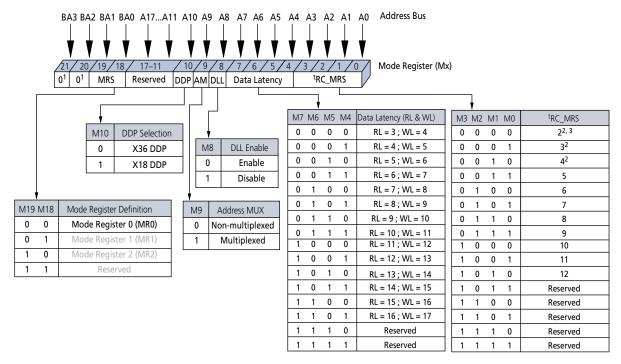

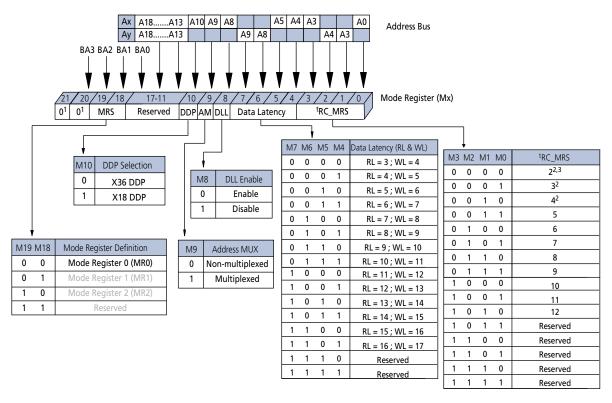

| Mode Register 0 (MR0)                                            | 26 |

| <sup>t</sup> RC                                                  | 26 |

| Data Latency                                                     | 26 |

| DLL Enable/Disable                                               | 26 |

| Address Multiplexing                                             | 27 |

| DDP Selection.                                                   | 27 |

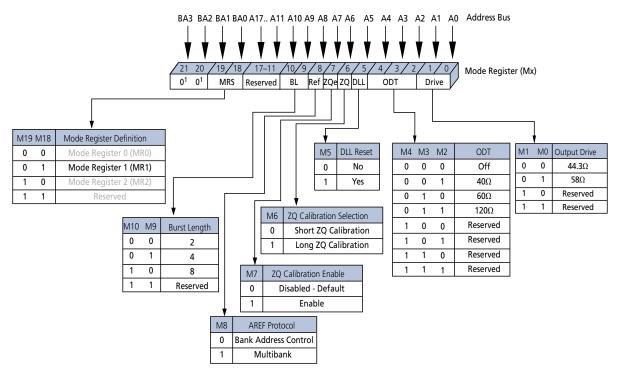

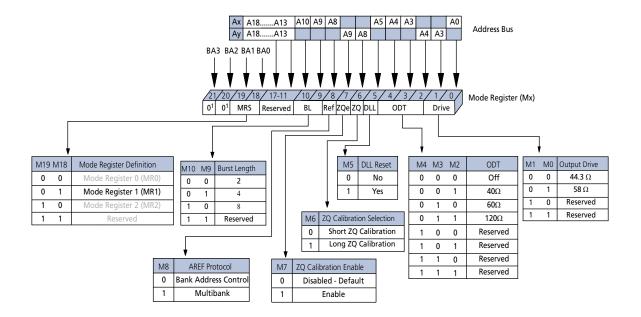

| Mode Register 1 (MR1)                                            |    |

| Output Drive Impedance                                           | 28 |

| On-Die Termination (ODT)                                         | 28 |

| ZQ Calibration                                                   |    |

| AUTO REFRESH Protocol                                            | 30 |

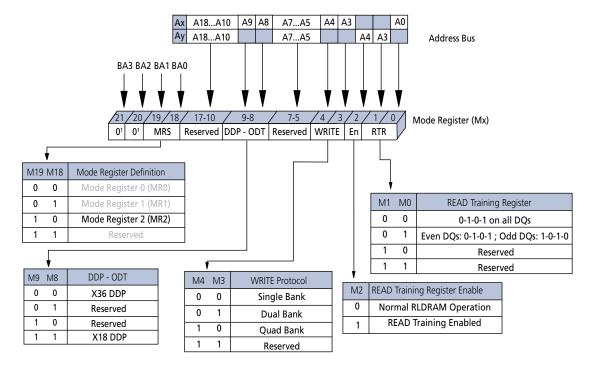

| Mode Register 2 (MR2)                                            |    |

| Dual Die Package - On Die Termination                            |    |

| READ Training Register                                           | 31 |

| INITIALIZATION Operation                                         | 34 |

| READ Operation                                                   | 36 |

| Multiplexed Address Mode                                         | 37 |

| Minney Town of an                                                | 40 |

### 1.125Gb: x18, x36 TwinDie RLDRAM 3 Features

# **List of Figures**

| Figure 1:  | 1Gb RLDRAM 3 Part Numbers                               | . 1 |

|------------|---------------------------------------------------------|-----|

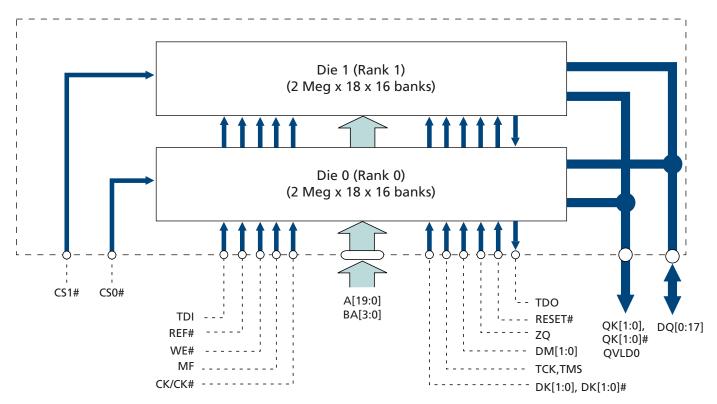

| Figure 2:  | 64 Meg x 18 Functional Block Diagram                    | . 7 |

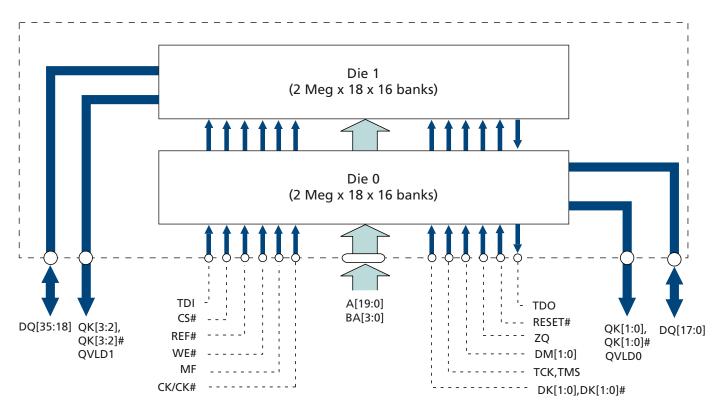

| Figure 3:  | 32 Meg x 36 Functional Block Diagram                    | . 8 |

| Figure 4:  | 168-Ball FBGA                                           | 12  |

| Figure 5:  | Output Driver                                           | 19  |

| Figure 6:  | MR0 Definition for Non-Multiplexed Address Mode         | 26  |

| Figure 7:  | MR1 Definition for Non-Multiplexed Address Mode         | 28  |

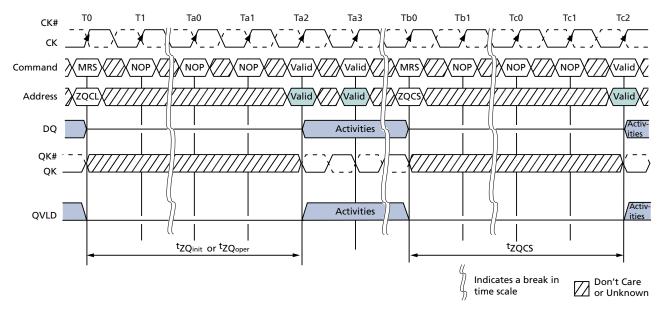

| Figure 8:  | ZQ Calibration Timing (ZQCL and ZQCS)                   | 30  |

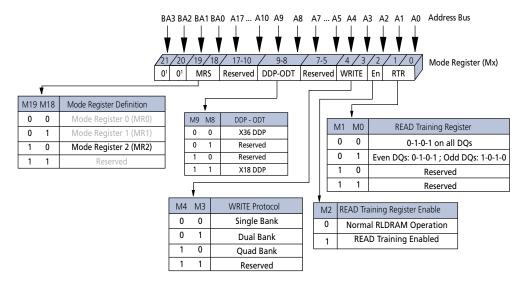

| Figure 9:  | MR2 Definition for Non-Multiplexed Address Mode         | 31  |

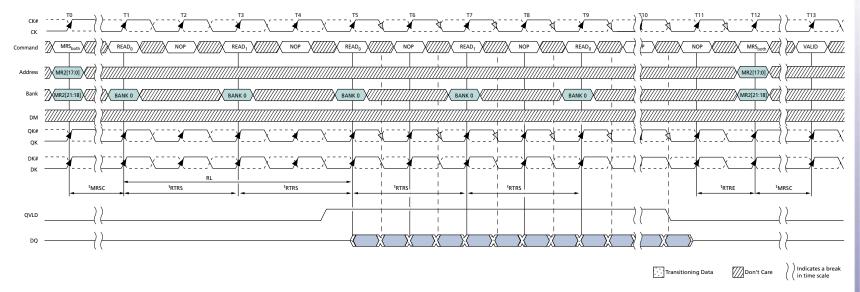

| Figure 10: | READ Training Function - x18 Die Interleave Training    | 33  |

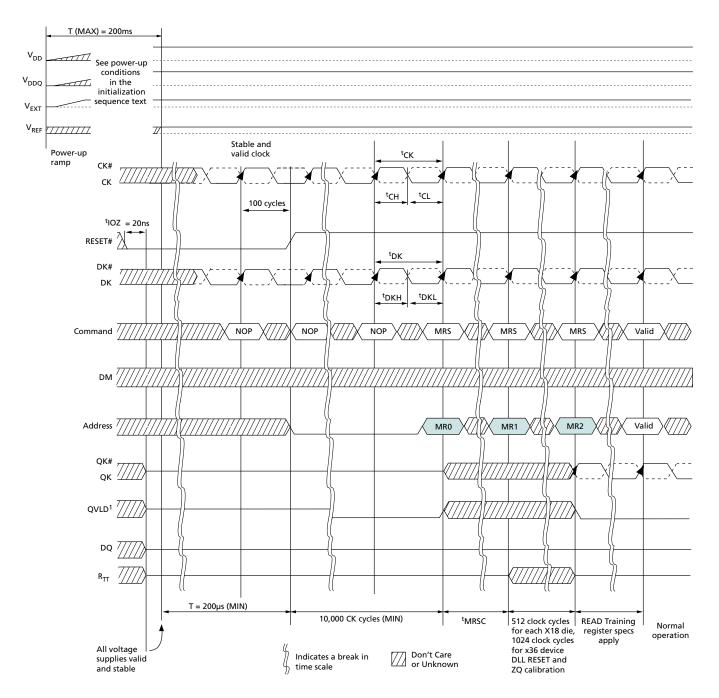

| Figure 11: | Power-Up/Initialization Sequence                        | 35  |

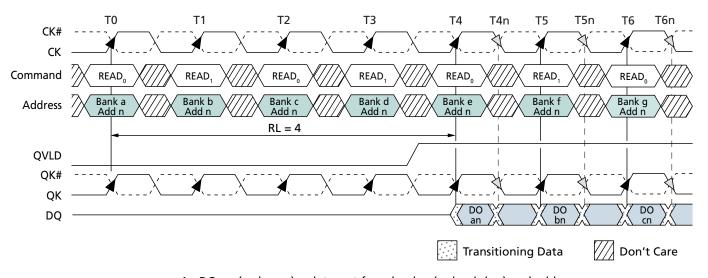

| Figure 12: | x18 Consecutive Die Interleave READ Bursts (BL = 2)     | 36  |

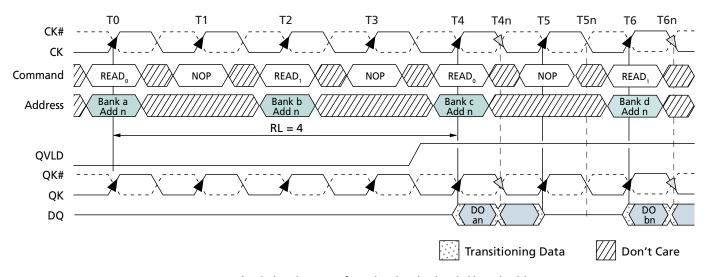

| Figure 13: | x18 Non-Consecutive Die Interleave READ Bursts (BL = 2) | 36  |

| Figure 14: | MR0 Definition for Multiplexed Address Mode             | 37  |

| Figure 15: | MR1 Definition for Multiplexed Address Mode             | 38  |

| Figure 16: | MR2 Definition for Multiplexed Address Mode             | 39  |

### 1.125Gb: x18, x36 TwinDie RLDRAM 3 Features

# **List of Tables**

| Table 1: 64 Meg x 18 Ball Assignments – 168-Ball FBGA (Top View)     |    |

|----------------------------------------------------------------------|----|

| Table 2: 32 Meg x 36 Ball Assignments – 168-Ball FBGA (Top View)     |    |

| Table 3: Ball Descriptions                                           | 10 |

| Table 4: x18 I <sub>DD</sub> Operating Conditions and Maximum Limits | 13 |

| Table 5: x36 I <sub>DD</sub> Operating Conditions and Maximum Limits | 14 |

| Table 6: Absolute Maximum Ratings                                    | 15 |

| Table 7: Input/Output Capacitance                                    | 15 |

| Table 8: R <sub>TT</sub> Effective Impedances                        | 16 |

| Table 9: R <sub>TT</sub> Effective Impedance Ranges                  | 16 |

| Table 10: ODT Sensitivity Definition                                 | 18 |

| Table 11: ODT Temperature and Voltage Sensitivity                    | 18 |

| Table 12: Driver Pull-Up and Pull-Down Impedance Calculations        | 19 |

| Table 13: Output Driver Sensitivity Definition                       |    |

| Table 14: Output Driver Voltage and Temperature Sensitivity          | 20 |

| Table 15: Single-Ended Output Driver Characteristics                 | 21 |

| Table 16: Differential Output Driver Characteristics                 | 21 |

| Table 17: DDP Timing adjustments                                     | 22 |

| Table 18: Thermal Impedance                                          | 23 |

| Table 19: Command Descriptions                                       | 24 |

| Table 20: x18 Command Table                                          |    |

| Table 21: x36 Command Table                                          | 25 |

| Table 22: Address Mapping in Multiplexed Address Mode                | 39 |

| Table 23: 64 Meg v 18 Ball Assignments with MF Ball Tied HIGH        | 40 |

### **General Description**

The 1Gb Micron® TwinDie RLDRAM® 3 is a high-speed memory device designed for high-bandwidth data storage—telecommunications, networking, cache applications, and so forth. Both the x18 and x36 configurations are composed of two 16-bank 576Mb RLDRAM 3 x18 devices. The TwinDie x18 RLDRAM 3 is a 2-rank device that shares address, control, and data signals between both die in the package. Separate CS# pins enable each of the ranks within the package. The TwinDie x36 RLDRAM 3 is a single-rank device that shares command, address, and control signals, but not the data bus.

The DDR I/O interface transfers two data bits per clock cycle at the I/O balls. Output data is referenced to the READ strobes.

Commands, addresses, and control signals are also registered at every positive edge of the differential input clock, while input data is registered at both positive and negative edges of the input data strobes.

Read and write accesses to the RL3 device are burst-oriented. The burst length (BL) is programmable to 2, 4, or 8 by a setting in the mode register.

The device is supplied with 1.35V for the core and 1.2V for the output drivers. The 2.5V supply is used for an internal supply.

Bank-scheduled refresh is supported, with the row address generated internally.

The 168-ball FBGA package is used to enable ultra-high-speed data transfer rates.

This data sheet provides a general description, package dimensions, and ballout as well as specifications that differ from the monolithic RLDRAM3 device. Refer to the Micron 576Mb RLDRAM 3 data sheet for complete information on power-up and initialization, command descriptions, and die operation.

# **Functional Block Diagrams**

Figure 2: 64 Meg x 18 Functional Block Diagram

Note: 1. Example for BL = 2; address bus width will be reduced with an increase in burst length.

Figure 3: 32 Meg x 36 Functional Block Diagram

Note: 1. Example for BL = 2; address bus width will be reduced with an increase in burst length.

## **Ball Assignments and Descriptions**

Table 1: 64 Meg x 18 Ball Assignments – 168-Ball FBGA (Top View)

|   | 1                | 2                | 3               | 4         | 5         | 6               | 7               | 8         | 9         | 10               | 11        | 12              | 13               |

|---|------------------|------------------|-----------------|-----------|-----------|-----------------|-----------------|-----------|-----------|------------------|-----------|-----------------|------------------|

| Α |                  | V <sub>SS</sub>  | $V_{DD}$        | NC        | $V_{DDQ}$ | NC <sup>1</sup> | $V_{REF}$       | DQ7       | $V_{DDQ}$ | DQ8              | $V_{DD}$  | V <sub>SS</sub> | RESET#           |

| В | V <sub>EXT</sub> | V <sub>SS</sub>  | NC              | $V_{SSQ}$ | NC        | $V_{DDQ}$       | DM0             | $V_{DDQ}$ | DQ5       | $V_{SSQ}$        | DQ6       | $V_{SS}$        | V <sub>EXT</sub> |

| С | $V_{DD}$         | NC               | $V_{DDQ}$       | NC        | $V_{SSQ}$ | NC              | DK0#            | DQ2       | $V_{SSQ}$ | DQ3              | $V_{DDQ}$ | DQ4             | V <sub>DD</sub>  |

| D | A11              | $V_{SSQ}$        | NC              | $V_{DDQ}$ | NC        | $V_{SSQ}$       | DK0             | $V_{SSQ}$ | QK0       | $V_{DDQ}$        | DQ0       | $V_{SSQ}$       | A13              |

| E | $V_{SS}$         | A0               | $V_{SSQ}$       | NC        | $V_{DDQ}$ | NC              | MF <sup>2</sup> | QK0#      | $V_{DDQ}$ | DQ1              | $V_{SSQ}$ | CS0#            | V <sub>SS</sub>  |

| F | A7               | CS1#             | $V_{DD}$        | A2        | A1        | WE#             | ZQ              | REF#      | A3        | A4               | $V_{DD}$  | A5              | A9               |

| G | $V_{SS}$         | A15              | A6              | $V_{SS}$  | BA1       | $V_{SS}$        | CK#             | $V_{SS}$  | BA0       | V <sub>SS</sub>  | A8        | A18             | V <sub>SS</sub>  |

| н | A19              | $V_{DD}$         | A14             | A16       | $V_{DD}$  | BA3             | CK              | BA2       | $V_{DD}$  | A17              | A12       | $V_{DD}$        | A10              |

| J | $V_{DDQ}$        | NC               | $V_{SSQ}$       | NC        | $V_{DDQ}$ | NC              | V <sub>SS</sub> | QK1#      | $V_{DDQ}$ | DQ9              | $V_{SSQ}$ | QVLD            | $V_{DDQ}$        |

| K | NC               | V <sub>SSQ</sub> | NC              | $V_{DDQ}$ | NC        | $V_{SSQ}$       | DK1             | $V_{SSQ}$ | QK1       | $V_{DDQ}$        | DQ10      | $V_{SSQ}$       | DQ11             |

| L | $V_{DD}$         | NC               | $V_{DDQ}$       | NC        | $V_{SSQ}$ | NC              | DK1#            | DQ12      | $V_{SSQ}$ | DQ13             | $V_{DDQ}$ | DQ14            | V <sub>DD</sub>  |

| М | V <sub>EXT</sub> | V <sub>SS</sub>  | NC              | $V_{SSQ}$ | NC        | $V_{DDQ}$       | DM1             | $V_{DDQ}$ | DQ15      | V <sub>SSQ</sub> | DQ16      | V <sub>SS</sub> | V <sub>EXT</sub> |

| N | V <sub>SS</sub>  | TCK              | V <sub>DD</sub> | TDO       | $V_{DDQ}$ | NC              | $V_{REF}$       | DQ17      | $V_{DDQ}$ | TDI              | $V_{DD}$  | TMS             | V <sub>SS</sub>  |

Notes:

- 1. NC balls for the x18 configuration are not connected to the DRAM die but do have parasitic capacitance associated with the package substrate. Balls may be connected to V<sub>SSO</sub>.

- 2. MF is assumed to be tied LOW for this ball assignment.

Table 2: 32 Meg x 36 Ball Assignments - 168-Ball FBGA (Top View)

|   | 1                | 2                                | 3         | 4               | 5         | 6         | 7                | 8         | 9         | 10              | 11        | 12              | 13               |

|---|------------------|----------------------------------|-----------|-----------------|-----------|-----------|------------------|-----------|-----------|-----------------|-----------|-----------------|------------------|

| Α |                  | V <sub>SS</sub>                  | $V_{DD}$  | DQ26            | $V_{DDQ}$ | DQ25      | $V_{REF}$        | DQ7       | $V_{DDQ}$ | DQ8             | $V_{DD}$  | V <sub>SS</sub> | RESET#           |

| В | V <sub>EXT</sub> | V <sub>SS</sub>                  | DQ24      | $V_{SSQ}$       | DQ23      | $V_{DDQ}$ | DM0              | $V_{DDQ}$ | DQ5       | $V_{SSQ}$       | DQ6       | V <sub>SS</sub> | V <sub>EXT</sub> |

| С | $V_{DD}$         | DQ22                             | $V_{DDQ}$ | DQ21            | $V_{SSQ}$ | DQ20      | DK0#             | DQ2       | $V_{SSQ}$ | DQ3             | $V_{DDQ}$ | DQ4             | V <sub>DD</sub>  |

| D | A11              | V <sub>SSQ</sub>                 | DQ18      | $V_{DDQ}$       | QK2       | $V_{SSQ}$ | DK0              | $V_{SSQ}$ | QK0       | $V_{DDQ}$       | DQ0       | $V_{SSQ}$       | A13              |

| E | V <sub>SS</sub>  | A0                               | $V_{SSQ}$ | DQ19            | $V_{DDQ}$ | QK2#      | MF <sup>2</sup>  | QK0#      | $V_{DDQ}$ | DQ1             | $V_{SSQ}$ | CS#             | V <sub>SS</sub>  |

| F | A7               | NF <sub>(CS1)</sub> <sup>1</sup> | $V_{DD}$  | A2              | A1        | WE#       | ZQ               | REF#      | A3        | A4              | $V_{DD}$  | A5              | A9               |

| G | V <sub>SS</sub>  | A15                              | A6        | V <sub>SS</sub> | BA1       | $V_{SS}$  | CK#              | $V_{SS}$  | BA0       | V <sub>SS</sub> | A8        | A18             | V <sub>SS</sub>  |

| Н | A19              | $V_{DD}$                         | A14       | A16             | $V_{DD}$  | BA3       | CK               | BA2       | $V_{DD}$  | A17             | A12       | $V_{DD}$        | A10              |

| J | $V_{DDQ}$        | QVLD1                            | $V_{SSQ}$ | DQ27            | $V_{DDQ}$ | QK3#      | V <sub>SS</sub>  | QK1#      | $V_{DDQ}$ | DQ9             | $V_{SSQ}$ | QVLD0           | $V_{DDQ}$        |

| K | DQ29             | V <sub>SSQ</sub>                 | DQ28      | $V_{DDQ}$       | QK3       | $V_{SSQ}$ | DK1              | $V_{SSQ}$ | QK1       | $V_{DDQ}$       | DQ10      | $V_{SSQ}$       | DQ11             |

| L | $V_{DD}$         | DQ32                             | $V_{DDQ}$ | DQ31            | $V_{SSQ}$ | DQ30      | DK1#             | DQ12      | $V_{SSQ}$ | DQ13            | $V_{DDQ}$ | DQ14            | $V_{DD}$         |

| M | V <sub>EXT</sub> | V <sub>SS</sub>                  | DQ34      | $V_{SSQ}$       | DQ33      | $V_{DDQ}$ | DM1              | $V_{DDQ}$ | DQ15      | $V_{SSQ}$       | DQ16      | V <sub>SS</sub> | V <sub>EXT</sub> |

| N | V <sub>SS</sub>  | TCK                              | $V_{DD}$  | TDO             | $V_{DDQ}$ | DQ35      | V <sub>REF</sub> | DQ17      | $V_{DDQ}$ | TDI             | $V_{DD}$  | TMS             | V <sub>SS</sub>  |

Notes:

- 1. The location of the additional chip select (CS1) is required on the 1Gb RLDRAM 3 x18 DDP configuration. It is internally connected so it can mirror with the address signal, A5, when MF is asserted HIGH. It also has the parasitic characteristics of an address pin.

- 2. MF is assumed to be tied LOW for this ball assignment.

#### **Table 3: Ball Descriptions**

| Symbol                      | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[19:0]                     | Input  | Address inputs: A[19:0] define the row and column addresses for READ and WRITE operations. During a MODE REGISTER SET, the address inputs define the register settings, along with BA[3:0]. They are sampled at the rising edge of CK.                                                                                                                                                                                                                                                  |

| BA[3:0]                     | Input  | Bank address inputs: Select the internal bank to which a command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                      |

| CK/CK#                      | Input  | <b>Input clock:</b> CK and CK# are differential input clocks. Addresses and commands are latched on the rising edge of CK.                                                                                                                                                                                                                                                                                                                                                              |

| CS[0:1]#                    | Input  | <b>Chip select:</b> CS[0:1]# enables the command decoder when LOW and disables it when HIGH. The TwinDie x18 device uses CS0# and CS1# to enable and disable the command decoder of each rank. The TwinDie x36 device has only a single CS# pin whereby the command decoder of both die are enabled and disabled simultaneously. When the command decoder is disabled, new commands are ignored, but internal operations continue.                                                      |

| DQ[35:0]                    | I/O    | <b>Data input:</b> The DQ signals form the 36-bit data bus. During READ commands, the data is referenced to both edges of QK. During WRITE commands, the data is sampled at both edges of DK.                                                                                                                                                                                                                                                                                           |

| DKx, DKx#                   | Input  | <b>Input data clock:</b> DKx and DKx# are differential input data clocks. All input data is referenced to both edges of DKx. For the x36 device, DQ[8:0] and DQ[26:18] are referenced to DK0 and DK0#, and DQ[17:9] and DQ[35:27] are referenced to DK1 and DK1#. For the x18 device, DQ[8:0] are referenced to DK0 and DK0#, and DQ[17:9] are referenced to DK1 and DK1#. DKx and DKx# are free-running signals and must always be supplied to the device.                             |

| DM[1:0]                     | Input  | <b>Input data mask:</b> DM is the input mask signal for WRITE data. Input data is masked when DM is sampled HIGH. DM0 is used to mask the lower byte for the x18 device and DQ[8:0] and DQ[26:18] for the x36 device. DM1 is used to mask the upper byte for the x18 device and DQ[17:9] and DQ[35:27] for the x36 device. Tie DM[1:0] to V <sub>SS</sub> if not used.                                                                                                                  |

| TCK                         | Input  | <b>IEEE 1149.1 clock input:</b> This ball must be tied to V <sub>SS</sub> if the JTAG function is not used.                                                                                                                                                                                                                                                                                                                                                                             |

| TMS, TDI                    | Input  | <b>IEEE 1149.1 test inputs:</b> These balls may be left as no connects if the JTAG function is not used.                                                                                                                                                                                                                                                                                                                                                                                |

| WE#, REF#                   | Input  | <b>Command inputs:</b> Sampled at the positive edge of CK, WE# and REF# (together with CS#) define the command to be executed.                                                                                                                                                                                                                                                                                                                                                          |

| RESET#                      | Input  | <b>Reset:</b> RESET# is an active LOW CMOS input referenced to $V_{SS}$ . RESET# assertion and deassertion are asynchronous. RESET# is a CMOS input defined with DC HIGH $\geq 0.8 \times V_{DDQ}$ and DC LOW $\leq 0.2 \times V_{DDQ}$ .                                                                                                                                                                                                                                               |

| ZQ                          | Input  | <b>External impedance:</b> This signal is used to tune the device's output impedance and ODT. RZQ needs to be $240\Omega$ , where RZQ is a resistor from this signal to ground.                                                                                                                                                                                                                                                                                                         |

| QK <i>x</i> , QK <i>x</i> # | Output | <b>Output data clocks:</b> QK and QK# are opposite-polarity output data clocks. They are free-running signals and during READ commands are edge-aligned with the DQs. For the x36 device, QK0, QK0# align with DQ[8:0]; QK1, QK1# align with DQ[17:9]; QK2, QK2# align with DQ[26:18]; and QK3, QK3# align with DQ[35:27]. For the x18 device, QK0, QK0# align with DQ[8:0]; QK1, QK1# align with DQ[17:9].                                                                             |

| QVLDx                       | Output | <b>Data valid:</b> The QVLD ball indicates that valid output data will be available on the subsequent rising clock edge. There is a single QVLD ball for the x18 device and two, QVLD0 and QVLD1, for the x36 device. QVLD0 aligns with DQ[17:0]; QVLD1 aligns with DQ[35:18].                                                                                                                                                                                                          |

| MF                          | Input  | <b>Mirror function:</b> The mirror function ball is a DC input used to create mirrored ballouts for simple dual-loaded clamshell mounting. If the ball is tied to $V_{SS}$ , the address and command balls are in their true layout. If the ball is tied to $V_{DDQ}$ , they are in the complement location. MF must be tied HIGH or LOW and cannot be left floating. MF is a CMOS input defined with DC HIGH $\geq 0.8 \text{ x}$ $V_{DD}$ and DC LOW $\leq 0.2 \text{ x}$ $V_{DDQ}$ . |

#### **Table 3: Ball Descriptions (Continued)**

| Symbol           | Туре   | Description                                                                                                      |

|------------------|--------|------------------------------------------------------------------------------------------------------------------|

| TDO              | Output | IEEE 1149.1 test output: JTAG output. This ball may be left as no connect if the JTAG function                   |

|                  |        | is not used.                                                                                                     |

| $V_{DD}$         | Supply | Power supply: 1.35V nominal.                                                                                     |

| $V_{DDQ}$        | Supply | <b>DQ power supply:</b> 1.2V nominal. Isolated on the device for improved noise immunity.                        |

| V <sub>EXT</sub> | Supply | Power supply: 2.5V nominal.                                                                                      |

| $V_{REF}$        | Supply | <b>Input reference voltage:</b> V <sub>DDQ</sub> /2 nominal. Provides a reference voltage for the input buffers. |

| V <sub>SS</sub>  | Supply | Ground.                                                                                                          |

| $V_{SSQ}$        | Supply | DQ ground: Isolated on the device for improved noise immunity.                                                   |

| NC               | -      | No connect: These balls are not connected to the DRAM.                                                           |

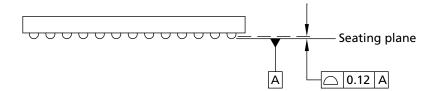

# **Package Dimensions**

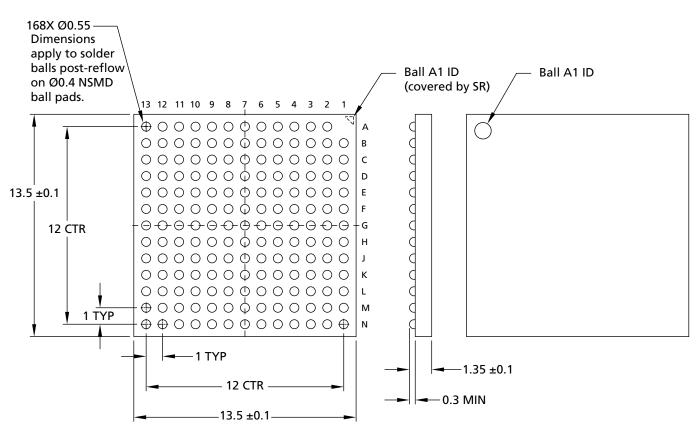

Figure 4: 168-Ball FBGA

Note: 1. All dimensions are in millimeters.

# **Electrical Characteristics - IDD Specifications**

Table 4: x18 I<sub>DD</sub> Operating Conditions and Maximum Limits

| <b>Combined Symbol</b>                       | Individual Die Status                                         | -107E | -107 | -125E | -125 | Units |

|----------------------------------------------|---------------------------------------------------------------|-------|------|-------|------|-------|

| I <sub>CSB1</sub> (V <sub>DD</sub> ) x18     | $I_{CSB1} = I_{SB1} + I_{SB1}$                                | 250   | 250  | 250   | 250  | mA    |

| I <sub>CSB1</sub> (V <sub>EXT</sub> ) x18    |                                                               | 60    | 60   | 60    | 60   |       |

| I <sub>CSB2</sub> (V <sub>DD</sub> ) x18     | $I_{CSB2} = I_{SB2} + I_{SB2}$                                | 1630  | 1630 | 1450  | 1450 | mA    |

| I <sub>CSB2</sub> (V <sub>EXT</sub> ) x18    |                                                               | 60    | 60   | 60    | 60   |       |

| I <sub>CDD1</sub> (V <sub>DD</sub> ) x18     | $I_{CDD1} = I_{DD1} + I_{SB2}$                                | 1915  | 1860 | 1665  | 1640 | mA    |

| I <sub>CDD1</sub> (V <sub>EXT</sub> ) x18    |                                                               | 65    | 65   | 65    | 65   |       |

| I <sub>CDD2</sub> (V <sub>DD</sub> ) x18     | $I_{CDD2} = I_{DD2} + I_{SB2}$                                | 1945  | 1890 | 1695  | 1670 | mA    |

| I <sub>CDD2</sub> (V <sub>EXT</sub> ) x18    |                                                               | 65    | 65   | 65    | 65   |       |

| I <sub>CDD3</sub> (V <sub>DD</sub> ) x18     | $I_{CDD3} = I_{DD3} + I_{SB2}$                                | 2015  | 1945 | 1755  | 1725 | mA    |

| I <sub>CDD3</sub> (V <sub>EXT</sub> ) x18    |                                                               | 65    | 65   | 65    | 65   |       |

| I <sub>CREF1</sub> (V <sub>DD</sub> ) x18    | I <sub>CREF1</sub> = I <sub>REF1</sub> + I <sub>SB2</sub>     | 2215  | 2215 | 1955  | 1955 | mA    |

| I <sub>CREF1</sub> (V <sub>EXT</sub> ) x18   |                                                               | 105   | 105  | 100   | 100  |       |

| I <sub>CREF2</sub> (V <sub>DD</sub> ) x18    | $I_{CREF2} = I_{REF2} + I_{SB2}$                              | 1635  | 1635 | 1435  | 1435 | mA    |

| I <sub>CREF2</sub> (V <sub>EXT</sub> ) x18   |                                                               | 60    | 60   | 60    | 60   |       |

| I <sub>CMBREF4</sub> (V <sub>DD</sub> ) x18  | I <sub>CMBREF4</sub> = I <sub>MBREF4</sub> + I <sub>SB2</sub> | 2845  | 2625 | 2610  | 2370 | mA    |

| I <sub>CMBREF4</sub> (V <sub>EXT</sub> ) x18 |                                                               | 145   | 145  | 135   | 135  |       |

| I <sub>CDD2W</sub> (V <sub>DD</sub> ) x18    | $I_{CDD2W} = I_{DD2W} + I_{SB2}$                              | 2725  | 2725 | 2390  | 2390 | mA    |

| I <sub>CDD2W</sub> (V <sub>EXT</sub> ) x18   |                                                               | 105   | 105  | 100   | 100  |       |

| I <sub>CDD4W</sub> (V <sub>DD</sub> ) x18    | $I_{CDD4W} = I_{DD4W} + I_{SB2}$                              | 2405  | 2405 | 2120  | 2120 | mA    |

| I <sub>CDD4W</sub> (V <sub>EXT</sub> ) x18   |                                                               | 85    | 85   | 80    | 80   |       |

| I <sub>CDD8W</sub> (V <sub>DD</sub> ) x18    | $I_{CDD8W} = I_{DD8W} + I_{SB2}$                              | 2150  | 2150 | 1915  | 1915 | mA    |

| I <sub>CDD8W</sub> (V <sub>EXT</sub> ) x18   |                                                               | 70    | 70   | 70    | 70   |       |

| I <sub>CDBWR</sub> (V <sub>DD</sub> ) x18    | $I_{CDBWR} = I_{DBWR} + I_{SB2}$                              | 2985  | 2985 | 2610  | 2610 | mA    |

| I <sub>CDBWR</sub> (V <sub>EXT</sub> ) x18   |                                                               | 105   | 105  | 100   | 100  |       |

| I <sub>CQBWR</sub> (V <sub>DD</sub> ) x18    | $I_{CQBWR} = I_{QBWR} + I_{SB2}$                              | 3705  | 3705 | 3250  | 3250 | mA    |

| I <sub>CQBWR</sub> (V <sub>EXT</sub> ) x18   |                                                               | 145   | 145  | 130   | 130  |       |

| I <sub>CDD2R</sub> (V <sub>DD</sub> ) x18    | $I_{CDD2R} = I_{DDR2} + I_{SB2}$                              | 2860  | 2860 | 2510  | 2510 | mA    |

| I <sub>CDD2R</sub> (V <sub>EXT</sub> ) x18   |                                                               | 105   | 105  | 100   | 100  |       |

| I <sub>CDD4R</sub> (V <sub>DD</sub> ) x18    | $I_{CDD4R} = I_{DDR4} + I_{SB2}$                              | 2410  | 2410 | 2125  | 2125 | mA    |

| I <sub>CDD4R</sub> (V <sub>EXT</sub> ) x18   |                                                               | 85    | 85   | 80    | 80   |       |

| I <sub>CDD8R</sub> (V <sub>DD</sub> ) x18    | $I_{CDD8R} = I_{DDR8} + I_{SB2}$                              | 2130  | 2130 | 1900  | 1900 | mA    |

| I <sub>CDD8R</sub> (V <sub>EXT</sub> ) x18   |                                                               | 70    | 70   | 70    | 70   |       |

Note: 1. I<sub>CDD</sub> values reflect the combined current of both individual die. I<sub>DDx</sub> and I<sub>SBx</sub> represent individual die values.

Table 5: x36 I<sub>DD</sub> Operating Conditions and Maximum Limits

| <b>Combined Symbol</b>                       | Individual Die Status                                            | -107E | -107 | -125E | -125 | Units |

|----------------------------------------------|------------------------------------------------------------------|-------|------|-------|------|-------|

| I <sub>CSB1</sub> (V <sub>DD</sub> ) x36     | $I_{CSB1} = I_{SB1} + I_{SB1}$                                   | 250   | 250  | 250   | 250  | mA    |

| I <sub>CSB1</sub> (V <sub>EXT</sub> ) x36    |                                                                  | 60    | 60   | 60    | 60   |       |

| I <sub>CSB2</sub> (V <sub>DD</sub> ) x36     | $I_{CSB2} = I_{SB2} + I_{SB2}$                                   | 1670  | 1670 | 1480  | 1480 | mA    |

| I <sub>CSB2</sub> (V <sub>EXT</sub> ) x36    |                                                                  | 60    | 60   | 60    | 60   |       |

| I <sub>CDD1</sub> (V <sub>DD</sub> ) x36     | $I_{CDD1} = I_{DD1} + I_{DD1}$                                   | 2220  | 2110 | 1880  | 1830 | mA    |

| I <sub>CDD1</sub> (V <sub>EXT</sub> ) x36    |                                                                  | 70    | 70   | 70    | 70   |       |

| I <sub>CDD2</sub> (V <sub>DD</sub> ) x36     | $I_{CDD2} = I_{DD2} + I_{DD2}$                                   | 2160  | 2060 | 1940  | 1890 | mA    |

| I <sub>CDD2</sub> (V <sub>EXT</sub> ) x36    |                                                                  | 70    | 70   | 70    | 70   |       |

| I <sub>CDD3</sub> (V <sub>DD</sub> ) x36     | $I_{CDD3} = I_{DD3} + I_{DD3}$                                   | NA    | NA   | NA    | NA   | mA    |

| I <sub>CDD3</sub> (V <sub>EXT</sub> ) x36    |                                                                  | NA    | NA   | NA    | NA   |       |

| I <sub>CREF1</sub> (V <sub>DD</sub> ) x36    | I <sub>CREF1</sub> = I <sub>REF1</sub> + I <sub>REF1</sub>       | 2840  | 2840 | 2460  | 2460 | mA    |

| I <sub>CREF1</sub> (V <sub>EXT</sub> ) x36   |                                                                  | 150   | 150  | 140   | 140  |       |

| I <sub>CREF2</sub> (V <sub>DD</sub> ) x36    | $I_{CREF2} = I_{REF2} + I_{REF2}$                                | 1635  | 1635 | 1485  | 1485 | mA    |

| I <sub>CREF2</sub> (V <sub>EXT</sub> ) x36   |                                                                  | 60    | 60   | 60    | 60   |       |

| I <sub>CMBREF4</sub> (V <sub>DD</sub> ) x36  | I <sub>CMBREF4</sub> = I <sub>MBREF4</sub> + I <sub>MBREF4</sub> | 4100  | 3660 | 3770  | 3290 | mA    |

| I <sub>CMBREF4</sub> (V <sub>EXT</sub> ) x36 |                                                                  | 230   | 230  | 210   | 210  |       |

| I <sub>CDD2W</sub> (V <sub>DD</sub> ) x36    | $I_{CDD2W} = I_{DD2W} + I_{DD2W}$                                | 4140  | 4140 | 3330  | 3330 | mA    |

| I <sub>CDD2W</sub> (V <sub>EXT</sub> ) x36   |                                                                  | 150   | 150  | 140   | 140  |       |

| I <sub>CDD4W</sub> (V <sub>DD</sub> ) x36    | $I_{CDD4W} = I_{DD4W} + I_{DD4W}$                                | 3330  | 3330 | 2790  | 2790 | mA    |

| I <sub>CDD4W</sub> (V <sub>EXT</sub> ) x36   |                                                                  | 110   | 110  | 100   | 100  |       |

| I <sub>CDD8W</sub> (V <sub>DD</sub> ) x36    | $I_{CDD8W} = I_{DD8W} + I_{DD8W}$                                | NA    | NA   | NA    | NA   | mA    |

| I <sub>CDD8W</sub> (V <sub>EXT</sub> ) x36   |                                                                  | NA    | NA   | NA    | NA   |       |

| I <sub>CDBWR</sub> (V <sub>DD</sub> ) x36    | $I_{CDBWR} = I_{DBWR} + I_{DBWR}$                                | 4500  | 4500 | 3770  | 3770 | mA    |

| I <sub>CDBWR</sub> (V <sub>EXT</sub> ) x36   |                                                                  | 150   | 150  | 140   | 140  |       |

| I <sub>CQBWR</sub> (V <sub>DD</sub> ) x36    | $I_{CQBWR} = I_{QBWR} + I_{QBWR}$                                | 6000  | 6000 | 5050  | 5050 | mA    |

| I <sub>CQBWR</sub> (V <sub>EXT</sub> ) x36   |                                                                  | 230   | 230  | 200   | 200  |       |

| I <sub>CDD2R</sub> (V <sub>DD</sub> ) x36    | $I_{CDD2R} = I_{DD2R} + I_{DD2R}$                                | 4360  | 4360 | 3570  | 3570 | mA    |

| I <sub>CDD2R</sub> (V <sub>EXT</sub> ) x36   |                                                                  | 150   | 150  | 140   | 140  |       |

| I <sub>CDD4R</sub> (V <sub>DD</sub> ) x36    | $I_{CDD4R} = I_{DD4R} + I_{DD4R}$                                | 3370  | 3370 | 2800  | 2800 | mA    |

| I <sub>CDD4R</sub> (V <sub>EXT</sub> ) x36   |                                                                  | 110   | 110  | 100   | 100  |       |

| I <sub>CDD8R</sub> (V <sub>DD</sub> ) x36    | $I_{CDD8R} = I_{DD8R} + I_{DD8R}$                                | NA    | NA   | NA    | NA   | mA    |

| I <sub>CDD8R</sub> (V <sub>EXT</sub> ) x36   |                                                                  | NA    | NA   | NA    | NA   |       |

Note: 1.  $I_{CDD}$  values reflect the combined current of both individual die.  $I_{DDx}$  and  $I_{SBx}$  represent individual die values.

# **Electrical Specifications – Absolute Ratings and I/O Capacitance**

### **Absolute Maximum Ratings**

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may adversely affect reliability.

**Table 6: Absolute Maximum Ratings**

| Symbol                            | Parameter                                                      | Min  | Мах   | Units |

|-----------------------------------|----------------------------------------------------------------|------|-------|-------|

| V <sub>DD</sub>                   | V <sub>DD</sub> supply voltage relative to V <sub>SS</sub>     | -0.4 | 1.975 | V     |

| $V_{DDQ}$                         | Voltage on V <sub>DDQ</sub> supply relative to V <sub>SS</sub> | -0.4 | 1.66  | V     |

| V <sub>IN</sub> ,V <sub>OUT</sub> | Voltage on any ball relative to V <sub>SS</sub>                | -0.4 | 1.66  | V     |

| V <sub>EXT</sub>                  | Voltage on V <sub>EXT</sub> supply relative to V <sub>SS</sub> | -0.4 | 2.8   | V     |

#### **Input/Output Capacitance**

#### **Table 7: Input/Output Capacitance**

Notes 1 and 2 apply to entire table

|                          | x18 DDP - 16                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                            | x36 DD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x36 DDP - 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                   | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Max                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C <sub>CK</sub>          | 4.25                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C <sub>DCK</sub>         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.15                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C <sub>IO</sub>          | 5.25                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C <sub>IO</sub>          | 5.25                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C <sub>IO</sub>          | 5.25                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |