## STM8S007xx STM8S20xxx Errata sheet

## STM8S007xx and STM8S20xxx device limitations

## Silicon identification

This errata sheet applies to revisions X, Y/6, V and W/7 of the STMicroelectronics STM8S007xx and STM8S20xxx products.

A full list of part numbers is shown in *Table 1*.

The products can be identified as shown in *Table 2*:

- By the revision code marked below the sales type on the device package

- By the last three digits of the Internal sales type printed on the box label

| Reference  | Part number                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STM8S007xx | STM8S007C8                                                                                                                                                          |

| STM8S207xx | STM8S207MB, STM8S207M8, STM8S207RB, STM8S207R8,<br>STM8S207R6, STM8S207CB, STM8S207C8, STM8S207C6,<br>STM8S207SB, STM8S207S8, STM8S207S6, STM8S207K8,<br>STM8S207K6 |

| STM8S208xx | STM8S208MB, STM8S208M8, STM8S208RB, STM8S208R8,<br>STM8S208R6, STM8S208CB, STM8S208C8, STM8S208C6,<br>STM8S208SB, STM8S208S8, STM8S208S6                            |

#### Table 2. Device identification

| Sales type | Revision code <sup>(1)</sup> marked on device |  |

|------------|-----------------------------------------------|--|

| STM8S007xx | V, W/7                                        |  |

| STM8S207xx | X, Y/6, V, W/7                                |  |

| STM8S208xx | A, 176, V, W/7                                |  |

1. Refer to Appendix A: Revision code on device marking for details on how to identify the revision code on the different packages.

## Contents

| 1 | Proc  | duct evolution      |                                                                                                             |  |

|---|-------|---------------------|-------------------------------------------------------------------------------------------------------------|--|

| 2 | Silic | on limit            | ations                                                                                                      |  |

|   | 2.1   | Core l              | imitations                                                                                                  |  |

|   |       | 2.1.1               | Activation level (AL) bit not functional in Halt mode                                                       |  |

|   |       | 2.1.2               | JRIL and JRIH instructions not available7                                                                   |  |

|   |       | 2.1.3               | Main CPU execution is not resumed after an ISR resets the AL bit7                                           |  |

|   |       | 2.1.4               | Unexpected DIV/DIVW instruction result in ISR8                                                              |  |

|   |       | 2.1.5               | Interrupt service routine (ISR) executed with priority of main process 8                                    |  |

|   | 2.2   | Syster              | m limitations                                                                                               |  |

|   |       | 2.2.1               | HSI RC oscillator cannot be switched off in Run mode9                                                       |  |

|   |       | 2.2.2               | LSI oscillator remains on in Active-halt mode when the AWU unit uses the HSE as input clock                 |  |

|   |       | 2.2.3               | Failure in CAN communication during bootloader9                                                             |  |

|   |       | 2.2.4               | RAM modified after reset by embedded bootloader9                                                            |  |

|   |       | 2.2.5               | Flash / EEPROM memory is read incorrectly after wakeup from power         down mode       10                |  |

|   | 2.3   | Timer               | peripheral limitations                                                                                      |  |

|   |       | 2.3.1               | Corruption of read sequence for the 16-bit counter registers                                                |  |

|   | 2.4   | UART                | peripheral limitations 11                                                                                   |  |

|   |       | 2.4.1               | PE testing issue in UART mode                                                                               |  |

|   |       | 2.4.2               | LIN mode: LIN header error when automatic resynchronization is enabled                                      |  |

|   |       | 2.4.3               | LIN mode: framing error with data byte 0x00                                                                 |  |

|   |       | 2.4.4               | LIN mode: framing error when receiving an identifier (ID)                                                   |  |

|   |       | 2.4.5               | LIN mode: parity error when receiving an identifier (ID)                                                    |  |

|   |       | 2.4.6               | LIN mode: OR flag not correctly set in LIN master mode                                                      |  |

|   | 2.5   | I <sup>2</sup> C pe | ripheral limitations                                                                                        |  |

|   |       | 2.5.1               | I <sup>2</sup> C event management14                                                                         |  |

|   |       | 2.5.2               | Corrupted last received data in I <sup>2</sup> C Master Receiver mode                                       |  |

|   |       | 2.5.3               | Wrong behavior of I <sup>2</sup> C peripheral in Master mode after misplaced STOP                           |  |

|   |       | 2.5.4               | Violation of $I^2C$ "setup time for repeated START condition" parameter $$ . 16                             |  |

|   |       | 2.5.5               | In I <sup>2</sup> C slave "NOSTRETCH" mode, underrun errors may not be detected and may generate bus errors |  |

| 3        | Revis | ion hist                    | ory                                                                                                         |  |

|----------|-------|-----------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Appendix | A Re  | evision                     | code on device marking 24                                                                                   |  |

|          |       | 2.8.1                       | PWM output available on two different ports (PC4 and PD7) when         TIM1_CH4 user option is set       23 |  |

|          | 2.8   | Miscella                    | neous                                                                                                       |  |

|          |       | 2.7.6                       | Write in beCAN paged registers ignored                                                                      |  |

|          |       | 2.7.5                       | beCAN read error in slow mode                                                                               |  |

|          |       | 2.7.4                       | beCAN transmitted data corruption                                                                           |  |

|          |       | 2.7.3                       | beCAN time triggered communication mode not supported 19                                                    |  |

|          |       | 2.7.2                       | beCAN woken up from Sleep mode with automatic wakeup interrupt 19                                           |  |

|          |       | 2.7.1                       | beCAN transmission error when Sleep mode is entered during transmission or reception                        |  |

|          | 2.7   | beCAN                       | peripheral limitations                                                                                      |  |

|          |       | 2.6.2                       | Busy flag is not reliable when the SPI is a master simplex receiver $\dots$ 18                              |  |

|          |       | 2.6.1                       | Last bit sent is too short if the SPI is disabled during communication $\ .$ . 18                           |  |

|          | 2.6   | SPI peripheral limitations1 |                                                                                                             |  |

|          |       | 2.5.6                       | $I^2C$ pulse missed $\ldots\ldots\ldots 17$                                                                 |  |

## **1 Product evolution**

*Table 3* gives a summary of the fix status.

Legend for *Table 3*: A = workaround available; N = no workaround available; P = partial workaround available, '-' and grayed = fixed.

| Section                                                                                        | Limitation                                                                                                       | Rev X | Rev Y/6, V,<br>W/7 |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|--------------------|

|                                                                                                | Section 2.1.1: Activation level (AL) bit not functional in Halt mode                                             | Ν     | N                  |

|                                                                                                | Section 2.1.2: JRIL and JRIH instructions not available                                                          | Ν     | N                  |

| Section 2.1: Core<br>limitations                                                               | Section 2.1.3: Main CPU execution is not resumed after an ISR resets the AL bit                                  | А     | A                  |

|                                                                                                | Section 2.1.4: Unexpected DIV/DIVW instruction result in ISR                                                     | А     | A                  |

|                                                                                                | Section 2.1.5: Interrupt service routine<br>(ISR) executed with priority of main<br>process                      | А     | A                  |

|                                                                                                | Section 2.2.1: HSI RC oscillator cannot be switched off in Run mode                                              | Ν     | N                  |

| Section 2.1.5: Interrupt<br>service routine (ISR)<br>executed with priority<br>of main process | Section 2.2.2: LSI oscillator remains on in<br>Active-halt mode when the AWU unit uses<br>the HSE as input clock | Ν     | N                  |

|                                                                                                | Section 2.2.3: Failure in CAN communication during bootloader                                                    | Ν     | -                  |

|                                                                                                | Section 2.2.4: RAM modified after reset<br>by embedded bootloader                                                | Ν     | -                  |

|                                                                                                | Section 2.2.5: Flash / EEPROM memory<br>is read incorrectly after wakeup from<br>power down mode                 | А     | A                  |

| Section 2.3: Timer peripheral limitations                                                      | Section 2.3.1: Corruption of read sequence for the 16-bit counter registers                                      | Ν     | N                  |

| Section                                                 | Limitation                                                                                                                          | Rev X | Rev Y/6, V,<br>W/7 |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|

|                                                         | Section 2.4.1: PE testing issue in UART mode                                                                                        | Ν     | N                  |

|                                                         | Section 2.4.2: LIN mode: LIN header error<br>when automatic resynchronization is<br>enabled                                         | N     | -                  |

| Section 2.3: Timer                                      | Section 2.4.3: LIN mode: framing error with data byte 0x00                                                                          | А     | A                  |

| peripheral limitations                                  | Section 2.4.4: LIN mode: framing error when receiving an identifier (ID)                                                            | А     | A                  |

|                                                         | Section 2.4.5: LIN mode: parity error when receiving an identifier (ID)                                                             | A     | A                  |

|                                                         | Section 2.4.6: LIN mode: OR flag not correctly set in LIN master mode                                                               | A     | A                  |

|                                                         | Section 2.5.1: I <sup>2</sup> C event management                                                                                    | А     | A                  |

|                                                         | Section 2.5.2: Corrupted last received data in I <sup>2</sup> C Master Receiver mode                                                | А     | A                  |

| Section 2.5: I <sup>2</sup> C<br>peripheral limitations | Section 2.5.3: Wrong behavior of I <sup>2</sup> C<br>peripheral in Master mode after<br>misplaced STOP                              | A     | A                  |

|                                                         | Section 2.5.4: Violation of I <sup>2</sup> C "setup time for repeated START condition" parameter                                    | А     | A                  |

|                                                         | Section 2.5.5: In I <sup>2</sup> C slave<br>"NOSTRETCH" mode, underrun errors<br>may not be detected and may generate<br>bus errors | A     | A                  |

|                                                         | Section 2.5.6: I <sup>2</sup> C pulse missed                                                                                        | А     | -                  |

| Section 2.6: SPI                                        | Section 2.6.1: Last bit sent is too short if the SPI is disabled during communication                                               | А     | A                  |

| peripheral limitations                                  | Section 2.6.2: Busy flag is not reliable when the SPI is a master simplex receiver                                                  | N     | N                  |

| Table 3. Product evolution summary | v (continued)         |

|------------------------------------|-----------------------|

|                                    | <b>y</b> (0011011000) |

| Section                                      | Limitation                                                                                                      | Rev X | Rev Y/6, V,<br>W/7 |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|--------------------|

| Section 2.7: beCAN<br>peripheral limitations | Section 2.7.1: beCAN transmission error<br>when Sleep mode is entered during<br>transmission or reception       | A     | A                  |

|                                              | Section 2.7.2: beCAN woken up from<br>Sleep mode with automatic wakeup<br>interrupt                             | А     | А                  |

|                                              | Section 2.7.3: beCAN time triggered communication mode not supported                                            | N     | N                  |

|                                              | Section 2.7.4: beCAN transmitted data corruption                                                                | А     | -                  |

|                                              | Section 2.7.5: beCAN read error in slow mode                                                                    | А     | А                  |

|                                              | Section 2.7.6: Write in beCAN paged registers ignored                                                           | A     | А                  |

| Section 2.8:<br>Miscellaneous                | Section 2.8.1: PWM output available on<br>two different ports (PC4 and PD7) when<br>TIM1_CH4 user option is set | Ν     | N                  |

| Table 3. Product evolu | tion summary (continued) |

|------------------------|--------------------------|

|------------------------|--------------------------|

## 2 Silicon limitations

### 2.1 Core limitations

#### 2.1.1 Activation level (AL) bit not functional in Halt mode

#### Description

The AL bit is not supported in Halt mode. In particular, when the AL bit of the CFG\_GCR register is set, the CPU does not return to Halt mode after exiting an interrupt service routine (ISR). It returns to the main program and executes the next instruction after the HALT instruction. The AL bit is supported correctly in WFI mode.

#### Workaround

No workaround available.

No fix is planned for this limitation.

#### 2.1.2 JRIL and JRIH instructions not available

#### Description

The JRIL (jump if port INT pin = 0) and JRIH (jump if port INT pin = 1) instructions are not supported by the devices covered by this errata sheet. These instructions perform conditional jumps: JRIL and JRIH jump if one of the external interrupt lines is low or high respectively.

In the devices covered by this errata sheet, JRIL is equivalent to an unconditional jump and JRIH is equivalent to NOP. For further details on these instructions, see the STM8 CPU programming manual (PM0044).

#### Workaround

No workaround available.

No fix is planned for this limitation.

#### 2.1.3 Main CPU execution is not resumed after an ISR resets the AL bit

#### Description

If the CPU is in wait for interrupt state and the AL bit is set, the CPU returns to wait for interrupt state after executing an ISR. To continue executing the main program, the AL bit must be reset by the ISR. When AL is reset just before exiting the ISR, the CPU may remain stalled.

#### Workaround

Reset the AL bit at least two instructions before the IRET instruction.

## 2.1.4 Unexpected DIV/DIVW instruction result in ISR

#### Description

In very specific conditions, a DIV/DIVW instruction may return a false result when executed inside an interrupt service routine (ISR). This error occurs when the DIV/DIVW instruction is interrupted and a second interrupt is generated during the execution of the IRET instruction of the first ISR. Under these conditions, the DIV/DIVW instruction executed inside the second ISR, including function calls, may return an unexpected result.

The applications that do not use the DIV/DIVW instruction within ISRs are not impacted.

### Workaround 1

If an ISR or a function called by this routine contains a division operation, the following assembly code should be added inside the ISR before the DIV/DIVW instruction:

push cc pop a and a,#\$BF push a pop cc

This sequence should be placed by C compilers at the beginning of the ISR using DIV/DIVW. Refer to your compiler documentation for details on the implementation and control of automatic or manual code insertion.

#### Workaround 2

To optimize the number of cycles added by workaround 1, you can use this workaround instead. Workaround 2 can be used in applications with fixed interrupt priorities, identified at the program compilation phase:

push #value

pop cc

where bits 5 and 3 of #value have to be configured according to interrupt priority given by I1 and I0, and bit 6 kept cleared.

In this case, compiler workaround 1 has to be disabled by using compiler directives.

No fix is planned for this limitation.

#### 2.1.5 Interrupt service routine (ISR) executed with priority of main process

#### Description

If an interrupt is cleared or masked when the context saving has already started, the corresponding ISR is executed with the priority of the main process. The next interrupt request can interrupt execution of the service routine

#### Workaround

At the beginning of the interrupt routine, change the current priority level in the CCR register by software.

### 2.2 System limitations

#### 2.2.1 HSI RC oscillator cannot be switched off in Run mode

#### Description

The internal 16 MHz RC oscillator cannot be switched off in run mode, even if the HSIEN bit is programmed to 0.

#### Workaround

No workaround available. No fix planned.

# 2.2.2 LSI oscillator remains on in Active-halt mode when the AWU unit uses the HSE as input clock

#### Description

When the auto wake-up unit (AWU) uses the high speed external clock (HSE) divided by the prescaler (clock source enabled by setting the CKAWUSEL option bit), the LSI RC oscillator is not switched off when the device operates in Active Halt mode with the main voltage regulator (MVR) on. This causes negligible extra power consumption compared to the total consumption of the MCU in Active Halt mode with the MVR on.

#### Workaround

No workaround available. No fix planned.

#### 2.2.3 Failure in CAN communication during bootloader

#### Description

The CAN filter registers are not initialized by the bootloader. This can lead to failure during communication with the bootloader.

#### Workaround

No workaround available.

#### 2.2.4 RAM modified after reset by embedded bootloader

#### Description

After each reset, the byte located at RAM address 0x99 is modified by the embedded bootloader even if the bootloader is disabled by option byte. So the RAM content at address 0x99 is not maintained after reset. The limitation is present only in device revision X.

#### Workaround

No workaround available. Do not use byte in RAM at address 0x99 to store variables which should be unchanged after device reset.

# 2.2.5 Flash / EEPROM memory is read incorrectly after wakeup from power down mode

#### Description

If Flash/EEPROM memory has been put in power down mode ( $I_{DDQ}$ ), the first read access after wakeup could return incorrect content when  $f_{CPU}$  is greater than 250 kHz + 5% and the number of wait states is configured to 0.

By default, the Flash/EEPROM memory is put in  $I_{DDQ}$  mode when the MCU enters Halt mode and depending on the FLASH\_CR1 register settings made by software, the Flash/EEPROM may be forced to  $I_{DDQ}$  mode during active halt mode.

As a consequence, the following behavior may be seen on some devices:

- After wakeup from Low power mode, with Flash memory in I<sub>DDQ</sub> mode, program execution gets lost due to an incorrect read of the vector table.

- Code reads an incorrect value from Flash/EEPROM memory, when forced in I<sub>DDQ</sub> mode.

- Reset could be forced by an illegal opcode execution due to incorrect read of instruction.

Note: The use of the watchdog helps the application to recover in case of failure.

#### Workaround 1

Keep the Flash/EEPROM in operating mode when MCU is put in Halt mode or Active-halt mode. This is done by configuring both the HALT and AHALT bits in the FLASH\_CR1 register before executing a HALT instruction to prevent the Flash/EEPROM entering  $I_{DDQ}$  mode.

Set HALT (bit 3) to '1':

- 0: Flash in power-down mode when MCU is in Halt mode

- 1: Flash in operating mode when MCU is in Halt mode

Keep AHALT (bit 2) at '0':

- 0: Flash in operating mode when MCU is in Active-halt mode

- 1: Flash in power-down when MCU is in Active-halt mode

Please refer to the datasheet for details on the impact on current consumption and wakeup time.

#### Workaround 2

Reduce  $f_{CPU}$  frequency to 250 kHz or lower before entering Low power mode to ensure correct Flash memory wakeup. This may be done using the clock divider (CPUDIV[2:0] bits in the CLK\_CKDIVR register). The clock divider can be reconfigured back to its previous state by software after wakeup.

This is illustrated by the following code example, assuming no divider is used in the application by default.

CLK\_CKDIVR = 0x06; \_asm("HALT"); CLK CKDIVR = 0x00;

The interrupt service routine executed after wakeup could either stay at the slower clock speed, or reconfigure the clock setting. Care has to be taken to restore the previous clock divider setting at the end of interrupt routines when modifying the clock divider.

#### Workaround 3

Set the number of wait states to 1.

This may be done by setting OPT7 to 0x01.

### 2.3 Timer peripheral limitations

#### 2.3.1 Corruption of read sequence for the 16-bit counter registers

#### Description

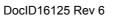

An 8-bit buffer is implemented for reading the 16-bit counter registers. Software must read the MS byte first, after which the LS byte value is buffered automatically (see *Figure 1*). This buffered value remains unchanged until the 16-bit read sequence is completed.

When any multi-cycle instruction precedes the read of the LSB, the content of the buffer is lost and the second read returns the immediate content of the counter directly.

Figure 1. 16-bit read sequence for the counter (TIMx\_CNTR)

#### Workaround

Do not use multi-cycle instructions before reading the LSB.

No fix is planned for this limitation.

## 2.4 UART peripheral limitations

#### 2.4.1 PE testing issue in UART mode

#### Description

When the RXNE flag is not polled, the device is in overrun condition and the PE flag does not rise in case of a parity error. The flag rises only for the last data which have been correctly received.

#### Workaround

No workaround available.

No fix is planned for this limitation.

# 2.4.2 LIN mode: LIN header error when automatic resynchronization is enabled

#### Description

If UART3 is configured in LIN slave mode (LSLV bit set in UART3\_CR6 register) and the automatic resynchronization is enabled (LASE bit set in UART3\_CR6), the LHE flag may be set instead of LHDF flag when receiving a valid header.

#### Workaround

No workaround available.

#### 2.4.3 LIN mode: framing error with data byte 0x00

#### Description

If the UART3 interface is configured in LIN slave mode, and the active mode with break detection length is set to 11 (LBDL bit of UART3\_CR4 register set to 1), FE and RXNE flags are not set when receiving a 0x00 data byte with a framing error, followed by a recessive state. This occurs only if the dominant state length is between 9.56 and 10.56 times the baud rate.

#### Workaround

The LIN software driver can handle this exceptional case by implementing frame timeouts to comply with the LIN standard. This method has been implemented in ST LIN 2.1 driver package which passed the LIN compliance tests.

#### 2.4.4 LIN mode: framing error when receiving an identifier (ID)

#### Description

If an ID framing error occurs when the UART3, configured in LIN mode, is in active mode, both the LHE and LHDF flags are set at the end of the LIN header with an ID framing error.

#### Workaround

The LIN software driver can handle this case by checking both the LHE and LHDF flags upon header reception.

No fix is planned for this limitation.

#### 2.4.5 LIN mode: parity error when receiving an identifier (ID)

#### Description

If an ID parity error occurs, the UART3, configured in LIN mode, wakes up from mute mode and both LHE and LHDF are set at the end of the LIN header with parity error. The PE flag is also set.

#### Workaround

The LIN software driver can handle this case by checking all flags upon header reception. No fix is planned for this limitation.

#### 2.4.6 LIN mode: OR flag not correctly set in LIN master mode

#### Description

When the UART operates in LIN master mode, the OR flag is not set if an overrun condition occurs. This is valid for all UARTs (1 to 3).

#### Workaround

The LIN software driver can detect this case through a LIN protocol error.

## 2.5 I<sup>2</sup>C peripheral limitations

### 2.5.1 I<sup>2</sup>C event management

#### Description

As described in the  $I^2C$  section of the STM8S and STM8A microcontroller reference manual (RM0016), the application firmware has to manage several software events before the current byte is transferred. If the EV7, EV7\_1, EV6\_1, EV6\_3, EV2, EV8, and EV3 events are not managed before the current byte is transferred, problems may occur such as receiving an extra byte, reading the same data twice, or missing data.

#### Workaround

When the EV7, EV7\_1, EV6\_1, EV6\_3, EV2, EV8, and EV3 events cannot be managed before the current byte transfer, and before the acknowledge pulse when the ACK control bit changes, it is recommended to use I<sup>2</sup>C interrupts in nested mode and to make them uninterruptible by increasing their priority to the highest priority in the application.

No fix is planned for this limitation.

## 2.5.2 Corrupted last received data in I<sup>2</sup>C Master Receiver mode

#### Conditions

In Master Receiver mode, when the communication is closed using method 2, the content of the last read data may be corrupted. The following two sequences are concerned by the limitation:

- Sequence 1: transfer sequence for master receiver when N = 2

- a) BTF = 1 (Data N-1 in DR and Data N in shift register)

- b) Program STOP = 1

- c) Read DR twice (Read Data N-1 and Data N) just after programming the STOP bit.

- Sequence 2: transfer sequence for master receiver when N > 2

- a) BTF = 1 (Data N-2 in DR and Data N-1 in shift register)

- b) Program ACK = 0

- c) Read Data N-2 in DR

- d) Program STOP bit to 1

- e) Read Data N-1.

#### Description

The content of the shift register (data N) is corrupted (data N is shifted 1 bit to the left) if the user software is not able to read data N-1 before the STOP condition is generated on the bus. In this case, reading data N returns a wrong value.

#### Workarounds

- Workaround 1

- Sequence 1

When sequence 1 is used to close communication using method 2, mask all active interrupts between STOP bit programming and Read data N-1.

– Sequence 2

When sequence 2 is used to close communication using method 2, mask all active interrupts between Read data N-2, STOP bit programming and Read data N-1.

Workaround 2

Manage I2C RxNE and TxE events with interrupts of the highest priority level, so that the condition BTF = 1 never occurs.

# 2.5.3 Wrong behavior of I<sup>2</sup>C peripheral in Master mode after misplaced STOP

#### Description

The I<sup>2</sup>C peripheral does not enter Master mode properly if a misplaced STOP is generated on the bus. This can happen in the following conditions:

- If a void message is received (START condition immediately followed by a STOP): the BERR (bus error) flag is not set, and the I<sup>2</sup>C peripheral is not able to send a START condition on the bus after writing to the START bit in the I2C\_CR2 register.

- In the other cases of a misplaced STOP, the BERR flag is set in the IC2\_CR2 register. If the START bit is already set in I2C\_CR2, the START condition is not correctly generated on the bus and can create bus errors.

#### Workaround

In the I<sup>2</sup>C standard, it is not allowed to send a STOP before the full byte is transmitted (8 bits + acknowledge). Other derived protocols like CBUS allow it, but they are not supported by the I<sup>2</sup>C peripheral.

In case of noisy environment in which unwanted bus errors can occur, it is recommended to implement a timeout to ensure that the SB (start bit) flag is set after the START control bit is set. In case the timeout has elapsed, the peripheral must be reset by setting the SWRST bit in the I2C\_CR2 control register. The I<sup>2</sup>C peripheral should be reset in the same way if a BERR is detected while the START bit is set in I2C\_CR2.

#### 2.5.4 Violation of I<sup>2</sup>C "setup time for repeated START condition" parameter

#### Description

In case of a repeated Start, the "setup time for repeated START condition" parameter (named  $t_{SU(STA)}$  in the datasheet and Tsu:sta in the I<sup>2</sup>C specifications) may be slightly violated when the I<sup>2</sup>C operates in Master Standard mode at a frequency ranging from 88 to 100 kHz.  $t_{SU(STA)}$  minimum value may be 4 µs instead of 4.7 µs.

The issue occurs under the following conditions:

- 1. The I<sup>2</sup>C peripheral operates in Master Standard mode at a frequency ranging from 88 to 100 kHz (no issue in Fast mode)

- 2. and the SCL rise time meets one of the following conditions:

- The slave does not stretch the clock and the SCL rise time is more than 300 ns (the issue cannot occur when the SCL rise time is less than 300 ns).

- or the slave stretches the clock.

#### Workaround

Reduce the frequency down to 88 kHz or use the  $I^2C$  Fast mode if it is supported by the slave.

# 2.5.5 In I<sup>2</sup>C slave "NOSTRETCH" mode, underrun errors may not be detected and may generate bus errors

#### Description

The data valid time ( $t_{VD;DAT}$ ,  $t_{VD;ACK}$ ) described by the I<sup>2</sup>C specifications may be violated as well as the maximum current data hold time ( $t_{HD;DAT}$ ) under the conditions described below. In addition, if the data register is written too late and close to the SCL rising edge, an error may be generated on the bus: SDA toggles while SCL is high. These violations cannot be detected because the OVR flag is not set (no transmit buffer underrun is detected).

This issue occurs under the following conditions:

- 1. The I<sup>2</sup>C peripheral operates In Slave transmit mode with clock stretching disabled (NOSTRETCH=1)

- 2. and the application is late to write the DR data register, but not late enough to set the OVR flag (the data register is written before the SCL rising edge).

#### Workaround

If the master device supports it, use the clock stretching mechanism by programming the bit NOSTRETCH=0 in the I2C\_CR1 register.

If the master device does not support it, ensure that the write operation to the data register is performed just after TXE or ADDR events. You can use an interrupt on the TXE or ADDR flag and boost its priority to the higher level.

Using the "NOSTRETCH" mode with a slow I<sup>2</sup>C bus speed can prevent the application from being late to write the DR register (second condition).

Note: The first data to be transmitted must be written into the data register after the ADDR flag is cleared, and before the next SCL rising edge, so that the time window to write the first data into the data register is less than  $t_{I OW}$ .

If this is not possible, a possible workaround can be the following:

- 1. Clear the ADDR flag

- 2. Wait for the OVR flag to be set

- 3. Clear OVR and write the first data.

The time window for writing the next data is then the time to transfer one byte. In that case, the master must discard the first received data.

### 2.5.6 I<sup>2</sup>C pulse missed

#### Description

When the  $I^2C$  interface is used for long transmit/receive transactions, the MCU may return a NACK somewhere during the transaction instead of returning an ACK for all data. The received data may also be corrupted. In Master mode the  $I^2C$  may not detect an incoming ACK. This is due to a weakness in the noise filter of the I/O pad which in certain conditions may cause the STM8  $I^2C$  to miss a pulse.

The workaround described below is not a clean solution. However, the limitation is fixed in revision Y/6 and W/7.

#### Workaround

Since data corruption is caused by noise generated by the CPU, CPU activity should be minimized during data reception and/or transmission. This is done by performing physical data transmission (Master mode) and reception (slave mode) in WFI state (wait for interrupt).

To allow the device to be woken up from WFI, I<sup>2</sup>C transmission and reception routines must be implemented through interrupt routines instead of polling mechanisms. Receive and transmit interrupts (received data processing) must be triggered only by the BTF bit flag (byte transfer finished) in the I2C\_SR1 register. This flag indicates that the I<sup>2</sup>C is in stretched state (data transfers are stretched on the bus).

Clock stretching must be enabled to allow data transfers from the slave to be stopped and to allow the CPU to be woken up to read the received byte.

To recover from possible errors, periodically check if the I<sup>2</sup>C does not remain in busy state for too long (BUSY bit set in I2C\_SR3 register). If so, it should be reinitialized.

Example of I<sup>2</sup>C slave code:

```

//...

//----

void main()

{

Init_I2C(); // init I2C to use interrupts: ITBUFEN=0, ITEVTEN=1,

ITERREN=1

while(1)

```

## 2.6 SPI peripheral limitations

#### 2.6.1 Last bit sent is too short if the SPI is disabled during communication

#### Description

When the SPI interface operates in master mode and the baud rate generator prescaler is equal to 2, the SPI is disabled during ongoing communications, and the data and clock output signals are switched off at the last strobing edge of the SPI clock.

Consequently, the length of the last bit is out of range and its reception on the bus is not ensured.

#### Workaround

Check if a communication is ongoing before disabling the SPI interface. This can be done by monitoring the BSY bit in the SPI\_SR register.

No fix is planned for this limitation.

#### 2.6.2 Busy flag is not reliable when the SPI is a master simplex receiver

#### Description

When the master is receiver only, it provides the clock immediately after setting the SPE bit in the SPI\_CR1 register. In this case, the clock is provided until the SPE bit is disabled, meaning that the SPI is always busy because it is in receiver mode only and continuously receives data from the clock. There is no need to read the BUSY bit to know the SPI status because as soon the SPI is enabled, it is BUSY.

Note: The SPE bit has no meaning when the SPI is in master receiver only mode.

#### Workaround

No workaround available.

## 2.7 beCAN peripheral limitations

# 2.7.1 beCAN transmission error when Sleep mode is entered during transmission or reception

#### Description

If beCAN Sleep operating mode entry is requested while a transmission or reception is ongoing, or a transmission request is pending, the CAN\_TX pin may have a spurious behavior, incompliant with the CAN protocol in case an error occurs on the bus.

No error frame will be sent and the device will enter Sleep mode.

#### Workaround

Before requesting Sleep mode, request Initialization mode and wait until Initialization mode is entered.

#### 2.7.2 beCAN woken up from Sleep mode with automatic wakeup interrupt

#### Description

Waking up the beCAN from Sleep mode using the automatic wakeup interrupt triggers an interrupt on each CAN Rx falling edge until the bus is idle.

#### Workaround

To have a wakeup interrupt triggered only on the first falling edge of the CAN Rx pin, perform the following actions:

- 1. Disable the automatic wakeup interrupt

- 2. Clear the WKUI flag

- 3. Disable the Sleep mode in the ISR

No fix planned.

#### 2.7.3 beCAN time triggered communication mode not supported

#### Description

The time triggered communication mode described in the STM8A reference manual (RM0016) is not supported.

TTCM bit must be kept at 0 in the CAN\_MCR register (time triggered communication mode disabled), and TGT bit in CAN\_MDLCR must be initialized to 0 (CAN\_MTSRH and CAN\_MTSRL registers not sent).

#### Workaround

No workaround available.

#### 2.7.4 beCAN transmitted data corruption

#### Description

The TGT bit can be set to 1 (CAN\_MTSRH and CAN\_MTSRL registers sent) even if the device is not in time triggered communication mode (TTCM set to 1). This is due to the fact that the CAN\_MDLCR register reset value is undefined, causing the TGT bit to be set to 1 whatever the value of TTCM. This leads to the corruption of last two data bytes sent.

#### Workaround

TGT bit in CAN\_MDLCR must be initialized to 0 (CAN\_MTSRH and CAN\_MTSRL registers not sent).

#### 2.7.5 beCAN read error in slow mode

#### Description

The read byte may be corrupted when the beCAN is in slow mode and a read operation is performed while a transmission is ongoing. This happens because the transmission mailboxes and the receive FIFOs share the same address/data lines for read and write operations.

#### Workaround

To prevent this problem from occurring, the CPU clock must be the master clock (CLK\_CKDIVR[2:0] = 000b) when the user application starts reading the FIFO (CPU clock divider changed to /1). After the FIFO read operation is complete, the CPU clock divider (slow mode) should be applied again.

No fix is planned for this limitation.

#### 2.7.6 Write in beCAN paged registers ignored

#### Description

In very specific conditions, a write to the beCAN paged registers may be ignored. This occurs when the CPU is writing twice or more into beCAN paged registers in consecutive master clock cycles, and during the second or further writes, the CAN 2.0B active core is accessing (read or write) one of the paged registers.

A typical case is when the CPU is writing constants into paged registers (typically a mailbox for transmission) while the CAN 2.0B active core is reading the filters during a frame reception, or writing the FIFO after a frame reception. The beCAN paged registers range is from address 0x5428 to address 0x5437.

Note: CAN 2.0B active core does not access the paged registers as long as the beCAN is in initialization mode. Therefore the issue cannot occur while the software is writing into the paged registers to initialize the beCAN (filter configuration, for example).

The CPU write into two paged registers in two consecutive master clock cycles may only happen in case of consecutive single-cycle load and transfer instructions or single-cycle bit operation instructions, when the destination is an address within the range 0x5428 to 0x5437 inside the beCAN peripheral. The instructions are single-cycle if the source is a constant (embedded in instruction opcode) or in the A accumulator (when the same value has to be stored in two or more CAN registers).

List of instructions:

MOV longmem, #byte ; LD longmem, A ; CLR longmem

#### **Examples:**

Consecutive MOV instructions with immediate addressing mode

```

MOV 0x5429, #0x08

MOV 0x542a, #0x0d

```

MOV 0x542b, #0x40

Consecutive LD instructions with A register as source

```

LD 0x542d, A

```

```

LD 0x542e, A

```

CLR instruction followed by another single-cycle instruction

```

CLR 0x542d

```

```

MOV 0x542e, #0x40

```

• Mix of single-cycle instructions

LD 0x5429, A MOV 0x542a, #0x0d

Consecutive single-cycle bit instruction BSET, BRST, BCPL might also generate the case.

#### List of instructions:

BSET longmem, n ; BRES longmem, n ; BCPL longmem, n

Another very unlikely case is indirect or indexed addressing with beCAN address loaded in X or Y registers, which also generates single-cycle instructions.

#### List of instructions:

```

LD (X), A ; LD (shortoff,X),A ; LD (longoff,X),A ; LD (Y), A ; LD (shortoff,

Y) ; LD (longoff, Y) ; CLR (X) ; CLR (shortoff,X) ; CLR (longoff,X) ; CLR (Y) ; CLR (shortoff,Y) ; CLR (longoff,Y) ; CLR (shortoff, SP)

```

This can also happen with a single 2-cycle LDW instruction, if two consecutive registers are written with a 16-bit data, with X or Y register as source.

#### List of instructions:

LDW longmem, X ; LDW longmem, Y

#### Example:

LDW 0x542a, X ; with X containing 0x0d40.

The issue may happen typically if the software is filling paged registers with constants.

#### Example:

```

#define MY_ID (unsigned int) 0x0350

[...]

CAN_MDLCR = 0x08;

CAN_MIDR1 = (MY_ID >> 6) & 0x1F;

CAN_MIDR2 = (MY_ID << 2) & 0xFC;

This generates the following code:

35085429 mov 0x5429, #8

350d542a mov 0x542a, #13

3540542b mov 0x542b, #64</pre>

```

If the beCAN paged registers are not written with constants, and if beCAN paged registers are written with the value of an 8-bit variable, this is very unlikely to fall into one of these cases, as either 2-cycle instructions are generated by the compiler or an additional instruction is inserted between two beCAN accesses (loading the variable into the A accumulator).

#### Impact on application

When all the specific conditions are met, a corrupted frame may be sent to the CAN bus.

#### Workaround

In case you need to write consecutively into paged registers, insert a NOP instruction in between each write. You can make use of inline assembly in C code.

#### Example:

```

#define MY_ID (unsigned int) 0x0350

[...]

CAN_P1 = 0x08;

_asm(nop");

CAN_P2 = (MY_ID >> 6) & 0x1F;

_asm(nop");

CAN_P3 = (MY_ID << 2) & 0xFC;</pre>

```

### 2.8 Miscellaneous

# 2.8.1 PWM output available on two different ports (PC4 and PD7) when TIM1\_CH4 user option is set

#### Description

When the TIM1\_CH4 alternate function remapping option is set (via option byte AFR4 bit), pulse-width modulation (PWM) output is available on both PC4 and PD7.

The TIM1\_CH4 option is reserved only for 44 pin packages where PC4 is not present.

#### Workaround

No workaround available.

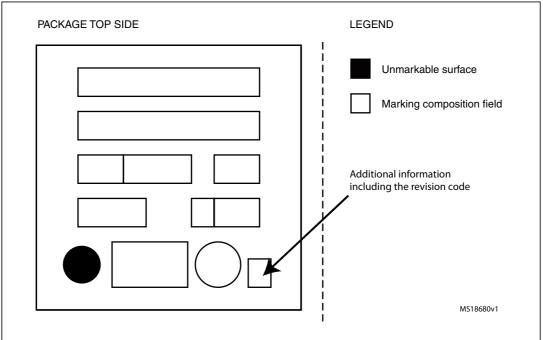

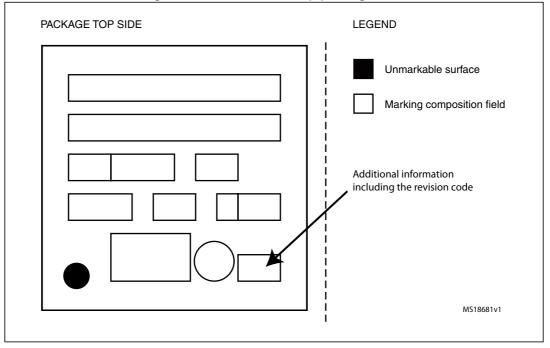

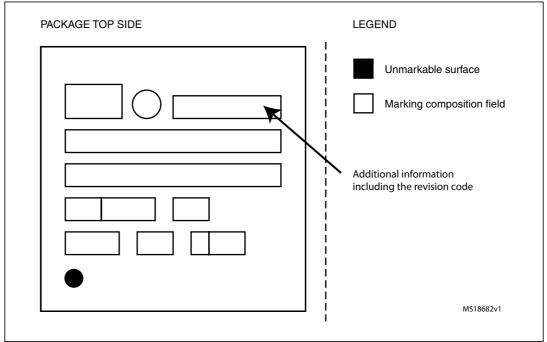

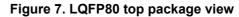

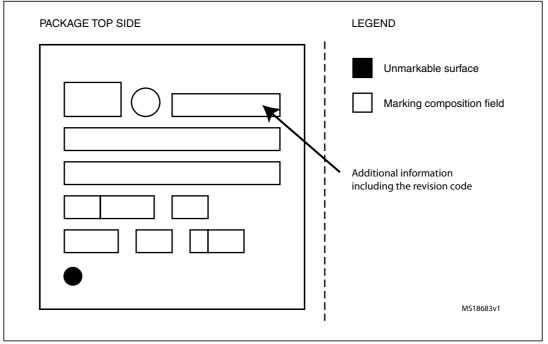

## Appendix A Revision code on device marking

The following figures show the standard marking compositions for the device packages. Only the Additional information field containing the revision code is shown.

Figure 2. LQFP32 top package view

Figure 3. LQFP44 top package view

Figure 4. LQFP48 top package view

#### Figure 5. LQFP64 10x10 top package view

Figure 6. LQFP64 14x14 top package view

## 3 Revision history

| Date                                                                                                                                                                                                                                                                                                                                                                                                     | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 07-Jul-2010                                                                                                                                                                                                                                                                                                                                                                                              | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 07-Mar-2011                                                                                                                                                                                                                                                                                                                                                                                              | 2        | <ul> <li>Added revision Y/6.</li> <li>Added Section 2.1.4: Unexpected DIV/DIVW instruction result in ISI and Section 2.4.3: LIN mode: framing error with data byte 0x00.</li> <li>Updated Section 2.5: I<sup>2</sup>C peripheral limitations and Appendix A: Revision code on device marking.</li> <li>Removed all references to UART2.</li> <li>Restructured document and changed layout of Table 3.</li> </ul> |  |

| 04-Jul-2011                                                                                                                                                                                                                                                                                                                                                                                              | 3        | Added revision W/7.<br>Updated Section 2.5.6: I <sup>2</sup> C pulse missed and Section 2.7.4: beCAN transmitted data corruption.                                                                                                                                                                                                                                                                                |  |

| 19-Mar-2012                                                                                                                                                                                                                                                                                                                                                                                              | 4        | Added reference STM8S007xx throughout the document.<br>Added Section 2.7.6: Write in beCAN paged registers ignored.                                                                                                                                                                                                                                                                                              |  |

| 14-Mar-2013                                                                                                                                                                                                                                                                                                                                                                                              | 5        | Updated Table 1: Device summary.<br>Modified Section 2.7.1: beCAN transmission error when Sleep mode<br>is entered during transmission or reception.                                                                                                                                                                                                                                                             |  |

| 06-Dec-2013       6         Added Section 2.1.5: Interrupt service routine (ISR) executed with priority of main process         Added Section 2.2.4: RAM modified after reset by embedded bootloader         Added Section 2.2.5: Flash / EEPROM memory is read incorrectly after wakeup from power down mode.         Added Section 2.3.1: Corruption of read sequence for the 16-bit counter registers |          |                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

#### Table 4. Document revision history

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com